Design and implementation 8 bit CPU architecture on Logisim for undergraduate learning support | Semantic Scholar

GitHub - tffdev/TSYS: 🍵🖥 A simple 12 bit Logisim RISC CPU architecture + a low-level programming language + an assembler

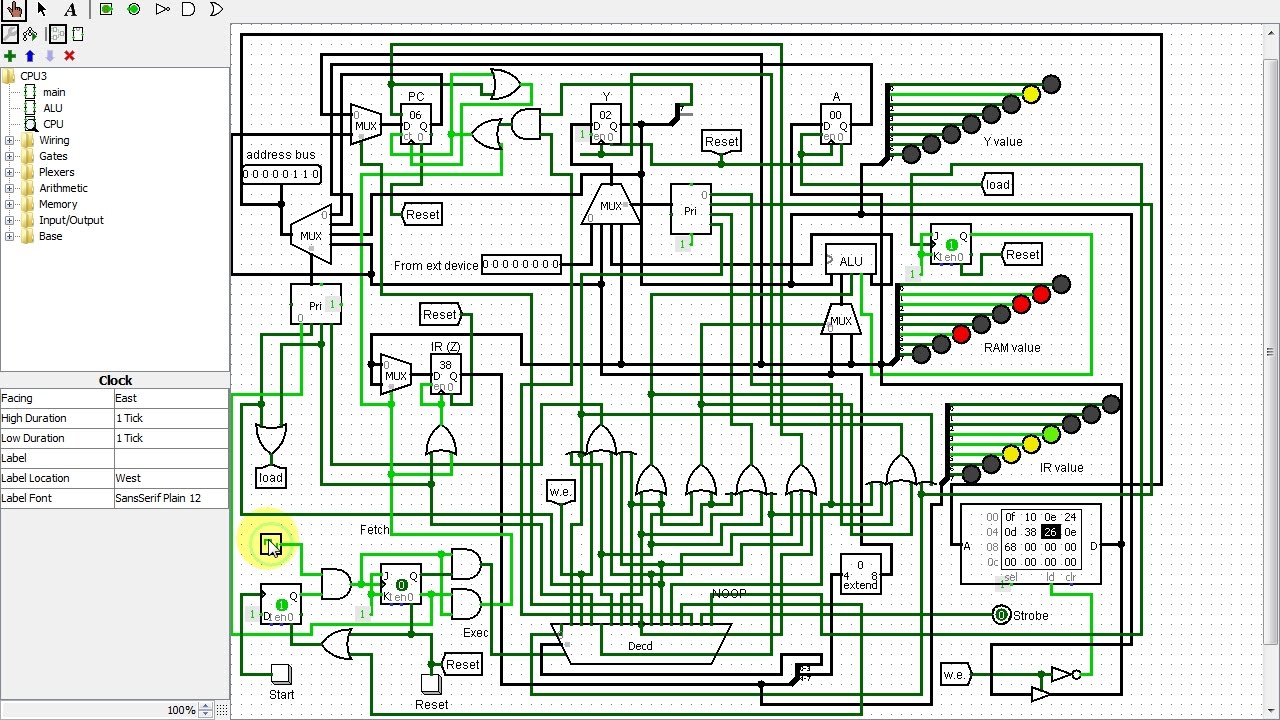

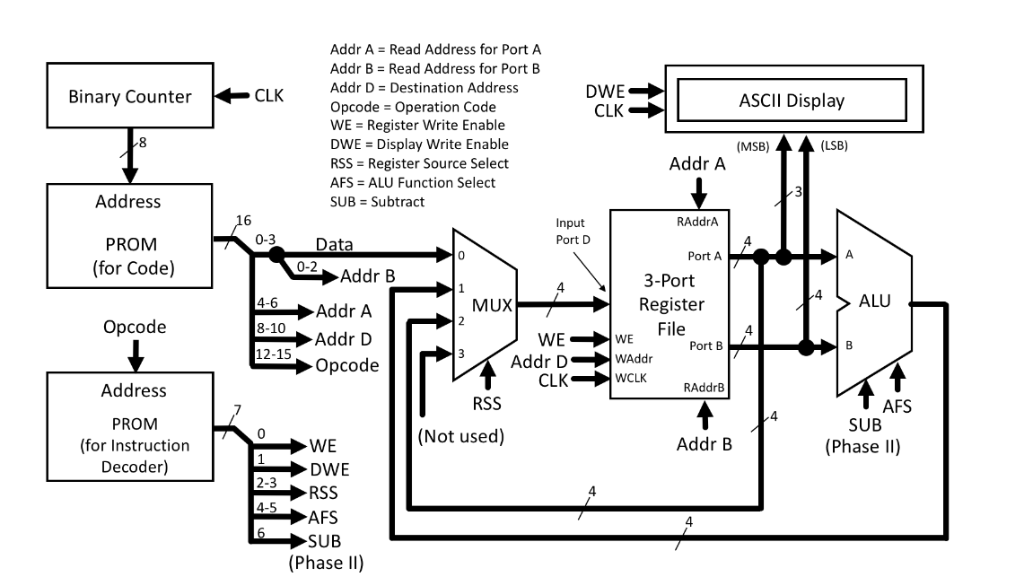

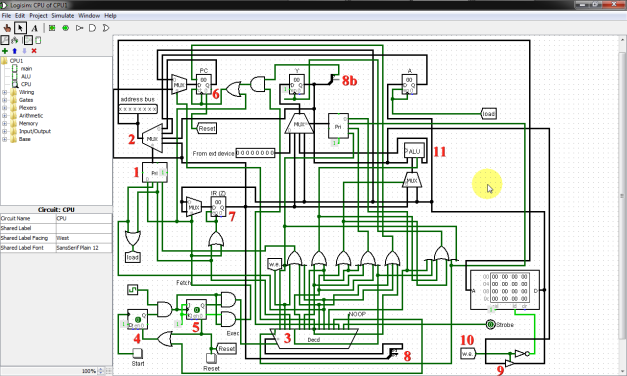

Step-by-step design and simulation of a simple CPU architecture | Proceeding of the 44th ACM technical symposium on Computer science education

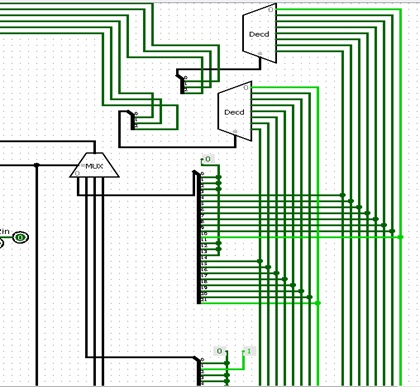

cpu - Logisim: Implementing a control unit for "Addition", "Logic bitwise AND" and "right logic shift" in ALU - Electrical Engineering Stack Exchange

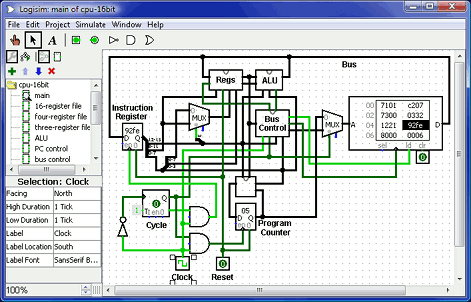

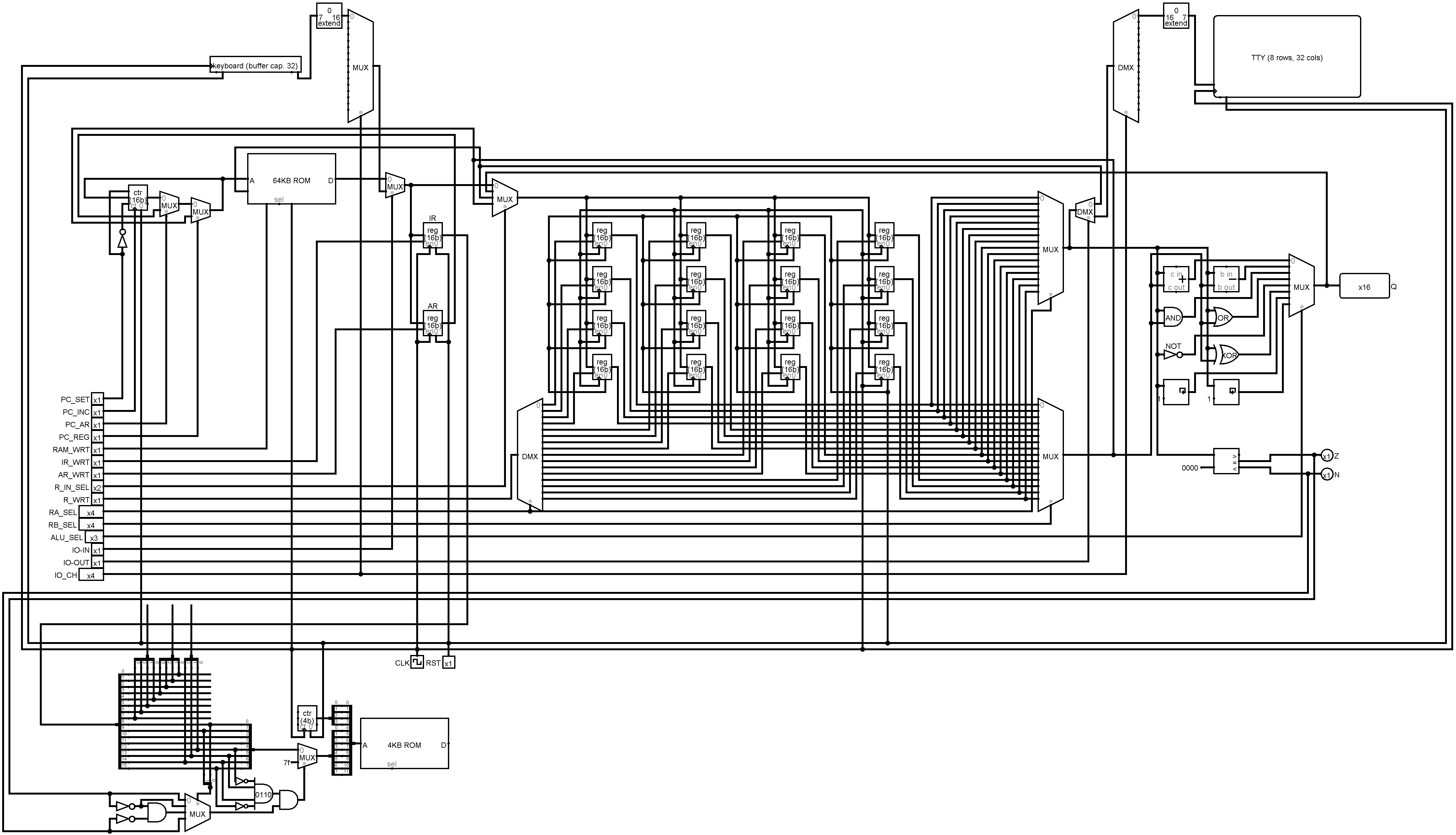

I recreated the 8-bit CPU in Logisim Evolution and upgraded it to a 16-bit and a 32-bit version which can also handle floats and has a more complex ALU and other useful