Dual-Core Lockstep enhanced with redundant multithread support and control-flow error detection - ScienceDirect

Comparing Lock-Step, redundant execution & Split-Lock - Embedded blog - Arm Community blogs - Arm Community

Applying dual core lockstep in embedded processors to mitigate radiation induced soft errors | Semantic Scholar

Electronics | Free Full-Text | Variable Delayed Dual-Core Lockstep (VDCLS) Processor for Safety and Security Applications

A Triple Core Lock-Step (TCLS) ARM® Cortex®-R5 Processor for Safety-Critical and Ultra-Reliable Applications | Semantic Scholar

Applying dual core lockstep in embedded processors to mitigate radiation induced soft errors | Semantic Scholar

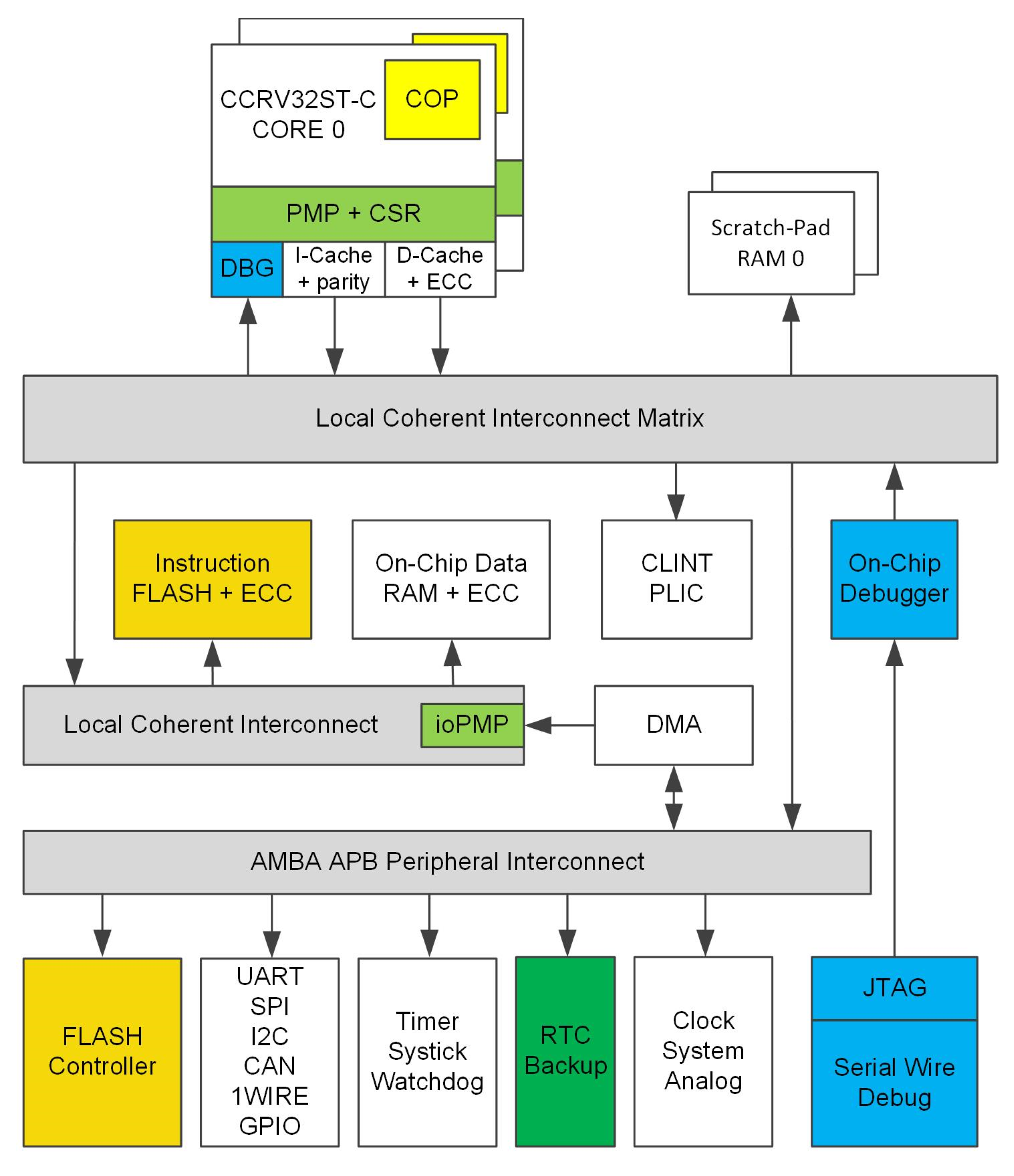

![Architecture of the lockstep system [27]. | Download Scientific Diagram Architecture of the lockstep system [27]. | Download Scientific Diagram](https://www.researchgate.net/publication/338851915/figure/fig9/AS:863244931584000@1582825038162/Architecture-of-the-lockstep-system-27.png)